W świeżo opublikowanym artykule w ONT autor opisuje proces dodania, a następnie programowania nowego układu za pomocą narzędzia HDL Coder.

O autorze

Autorem artykułu jest Arkadiusz Nerć, asystent Politechniki Morskiej w Szczecinie, pracujący na Wydziale Mechatroniki i Elektrotechniki w Katedrze Automatyki Okrętowej. Wydział ten, utworzony 1 października 2019 r., bazuje na dokonaniach dawnego Instytutu Elektrotechniki i Automatyki Okrętowej. Działające w jego strukturach Katedra Elektrotechniki i Energoelektroniki, Katedra Automatyki Okrętowej oraz Katedra Robotyki i Sterowania tworzą nowoczesną jednostkę badawczo-dydaktyczną, dostosowaną do wymogów współczesnego rynku technicznego szkolnictwa wyższego. Pracownicy katedr czynnie uczestniczą w licznych projektach badawczych, które skupiają się na wykorzystaniu zaawansowanych systemów energoelektronicznych w układach energetycznych statków i innych obiektów pływających. Prace te mają charakter zarówno symulacyjny, jak i laboratoryjny, a ich wyniki są regularnie publikowane w czasopismach, takich jak IEEE.Arkadiusz Nerć posiada bogate doświadczenie w pracy ze środowiskiem MATLAB & Simulink, także w zakresie układów FPGA i automatyki, co znacząco wzbogaca kontekst jego projektów o zaawansowaną wiedzę z tych dziedzin. Jako wykładowca, zajmuje się kształceniem przyszłych inżynierów, którzy mogą pracować zarówno na statkach morskich, jak i w lądowych firmach serwisowych w branżach elektrycznej, elektryczno-automatycznej i elektryczno-mechanicznej.

Opis problemu

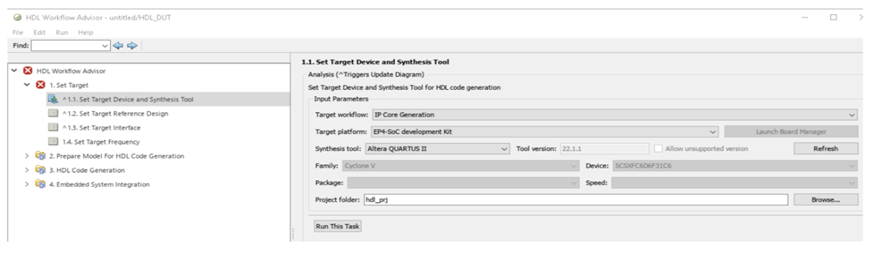

Projekt został zainicjowany w celu wykorzystania płytki rozwojowej FPGA Altera Cyclone IV EP4CE6 Waveshare 6483 na potrzeby zajęć dla studentów oraz w pracach badawczych. Jego głównym celem jest wdrożenie różnorodnych algorytmów na układach FPGA, które mogą znaleźć zastosowanie w automatyce okrętowej. Wyzwaniem była konfiguracja środowiska tak, aby cały proces implementacji wykonać z poziomu środowiska MATLAB i Simulink oraz narzędzia HDL Coder.Główne zadanie polegało na zapewnieniu sprawnej komunikacji z płytką wyposażoną w układ FPGA z rodziny Cyclone IV, która nie jest domyślnie dostępna na liście urządzeń do wyboru w tym środowisku. W załączonych plikach i instrukcjach znajdują się szczegółowe informacje na temat implementacji modelu i wygenerowania IP Core'a na urządzenie EP4CE6 przy użyciu HDL Codera i jego wiodącej aplikacji, czyli HDL Workflow Advisor.

Altera Cyclone IV EP4CE6 - płytka rozwojowa FPGA - Waveshare 6483

Żródło: https://botland.com.pl/

Rozwiązanie problemu

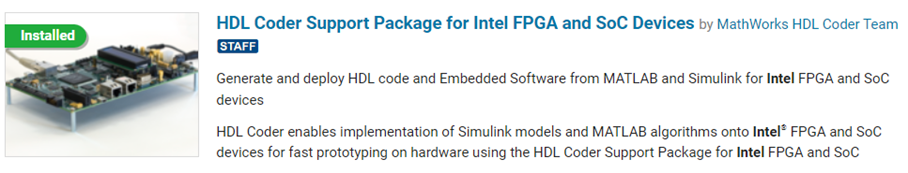

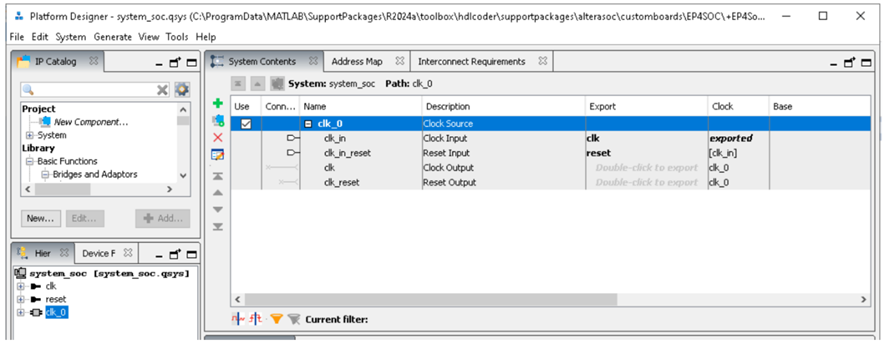

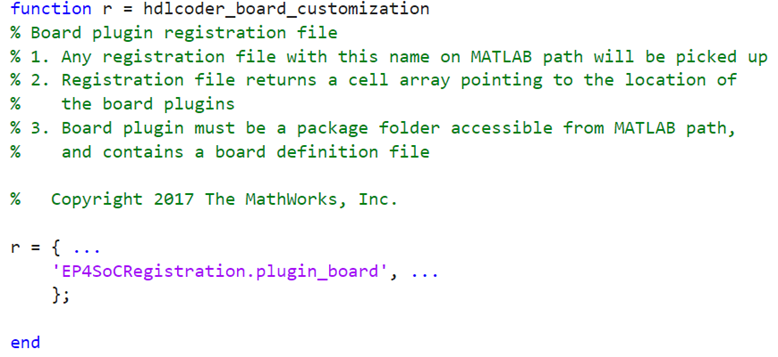

W celu rozwiązania problemu z generowaniem IP Core dla modelu FPGA core EP4CE6 przy użyciu HDL Codera, podjęto kilka kroków. Najpierw autor zapoznał się z dokumentacją MathWorks dotyczącą definiowania i rejestrowania własnych płyt oraz projektów referencyjnych dla układów Intel SoC oraz instrukcjami dotyczącymi przepływu pracy dla generowania IP Core bez procesora ARM, co było kluczowym elementem do zrozumienia całego procesu.Pełna obsługa wsparcia dla urządzeń FPGA wybranego producenta została zapewniona przez darmowy pakiet wsparcia „HDL Coder Support Package for Intel FPGA and SoC Devices”. Na podstawie dostępnego przykładu dla układu DE1SOC autor stworzył dedykowany plugin do posiadanego układu FPGA, np. EP4CE6E22C8N. Dzięki temu możliwe było dostosowanie i zoptymalizowanie narzędzi MATLAB & Simulink do pracy z wybraną płytką.

Kroki niezbędne do rozwiązania problemu:

1. Zapoznanie się z dokumentacją w celu zrozumienia procesu rejestrowania niestandardowej płytki.

- https://mathworks.com/help/hdlcoder/ug/define-and-register-custom-board-and-reference-design-for-intel-soc-workflow.html

- https://mathworks.com/help/hdlcoder/ug/ip-core-generation-workflow-without-an-embedded-arm-processor-arrow-deca-max-10-fpga-evaluation-kit.html

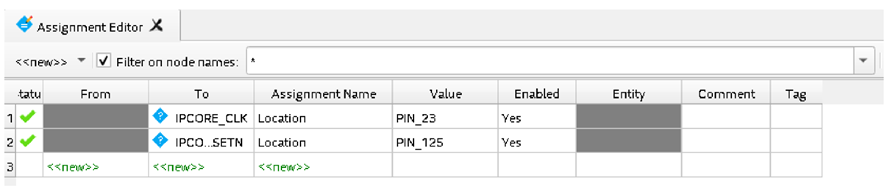

3. Wygenerowanie odpowiedniego pluginu w narzędziu Quartus dla wybranego FPGA (np. EP4CE6E22C8N).

4. Uzupełnienie szablonowych skryptów MATLABa w celu dodania układu i płytki do listy urządzeń gotowych do wykorzystania.

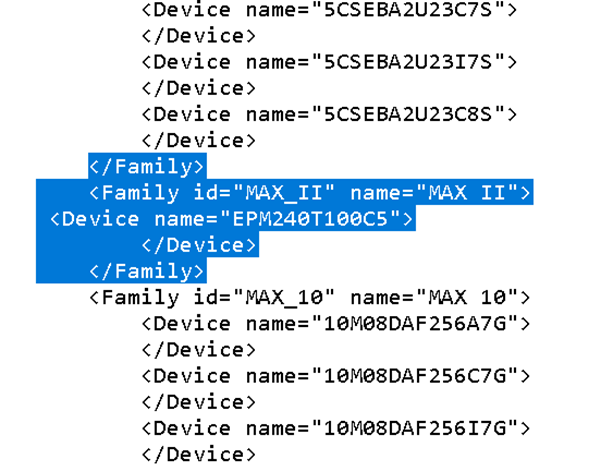

5. Aktualizacja listy urządzeń w razie braku obsługi dla układu.

C:\ProgramFiles\MATLAB\R2024a\toolbox\hdlcoder\hdlcommon\+downstreamtools\+AlteraQuartus_22_1_1\device_list.xml

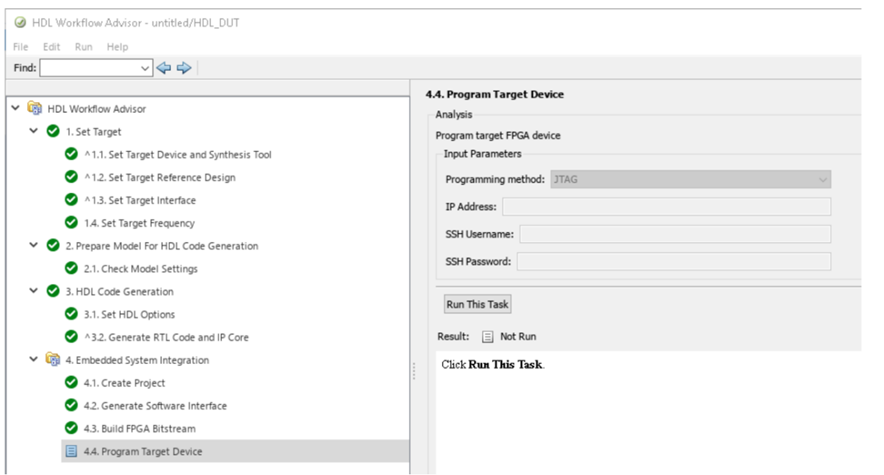

6. Generacja kodu i programowanie układu z poziomu asystenta HDL Workflow Advisor dla nowego urządzenia:

Podsumowanie

Ostatecznie projekt zakończył się sukcesem - kod z modelu Simulinka został wygenerowany, skompilowany i wgrany na układ w postaci bitstream'u, który zadziałał zgodnie z założeniami. Wykonanie każdego etapu pracy od zamodelowania algorytmu, aż po zaprogramowanie układu oraz komunikację z układem w czasie rzeczywistym zostało zrealizowane całościowo w środowisku MATLAB i Simulink, co znacznie przyspieszyło pracę i pozwoliło uniknąć ewentualnych błędów przy przenoszeniu danych do innego środowiska.Wyniki pokazują, że pełne wykorzystanie narzędzia Simulink do programowania FPGA z obsługą komunikacji i zewnętrznych I/O, jest możliwe i efektywne. Środowisko firmy MathWorks wspiera rozbudowę rozwiązań o niestandardowe komponenty sprzętowe i pozwala w łatwy sposób dodać je do listy wspieranych urządzeń.

Autor rozważa przetestowanie omawianego podejścia dla innych rodzin układów. Planuje także rozbudowę płytki o nowe peryferia, np. przetworniki (ADC, DAC) i kontynuację pracy z narzędziem HDL Coder.

Źródło: https://ont.com.pl/user_stories/od-modelu-do-FPGA#Oautorze